控制器局域网 局域网远程控制

来源: 最后更新:23-03-20 12:14:03

-

控制器局域网的概念

控制器局域网是国际上应用最广泛的现场总线之一。CAN被设计作为汽车环境中的微控制器通讯,在车载各电子控制装置ECU之间交换信息,形成汽车电子控制网络。比如:发动机管理系统、变速箱控制器、仪表装备、电子主干系统中,均嵌入CAN控制装置。 一个由CAN 总线构成的单一网络中,理论上可以挂接无数个节点。实际应用中,节点数目受网络硬件的电气特性所限制。例如,当使用Philips P82C250作为CAN收发器时,同一网络中允许挂接110个节点。CAN 可提供高达1Mbit/s的数据传输速率,这使实时控制变得非常容易。另外,硬件的错误检定特性也增强了CAN的抗电磁干扰能力。

控制器局域网(CAN)标准不断发展,正用于车载和工业网络之外的许多新应用。支持它的微处理器变得普遍且价格低廉,并且开源协议栈让其非常容易访问,同时也容易添加至新系统。有许多CAN板可用于BeagleBone (Capes)、Stellaris® (BoosterPacks)、Arduino (Shields)和其他微处理器开发平台。当设计人员的系统上电却不能工作时,应该怎么办呢?本文为您介绍一种对CAN物理层进行调试的较好工程方法。我们将介绍基础调试步骤,并说明一个CAN物理层应有的性能,以及找出问题的一些小技巧。

调试基础知识

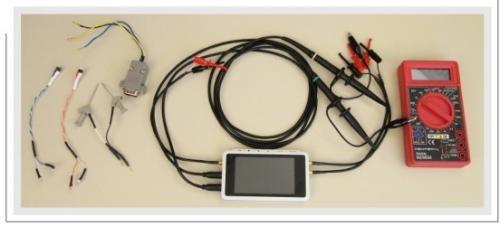

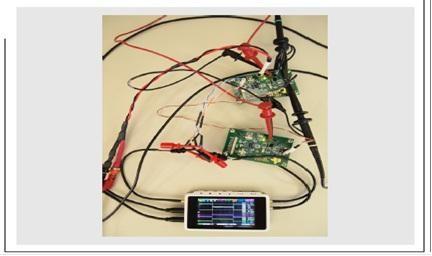

ISO11898-2和ISO11898-5规范详细说明了高速CAN物理层即收发器。掌握CAN物理层的基础知识以后,利用简单的调试工具便可迅速地找出常见问题。所需的基本实验室工具为示波镜、数字万用表(DMM)和一个电源。如果想要深入了解问题,则需要更高精度和更复杂的工具。这种问题已非本文讨论的范畴,但是这里介绍的基础知识可帮助确定问题所属类别,以及进一步调试所需的其他工具。一个由 TI 组装的CAN演示系统以及TI的SN65NVD255D评估模块(EVM)1,用于演示硬件。另外,我们还使用了其他一些东西,例如:CAN连接器外接头电缆和芯片钩(抓住收发器引脚,让其连接至电缆,以更加容易地连接示波器指针,如图1所示)。图1 CAN物理层调试基本工具

连接检查

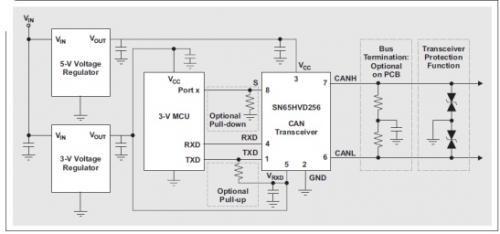

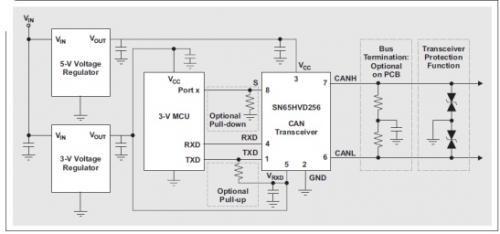

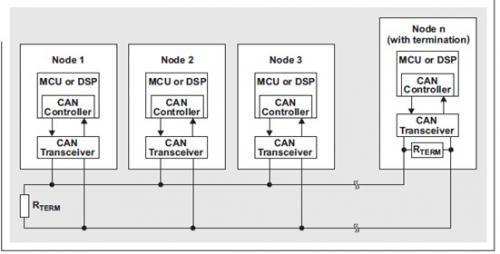

开始调试对话时,使用DMM确认印刷电路板(PCB)上连接如我们所预计的那样—系统未上电。这看似很基础,但令人吃惊的是,这个简单的方法却解决了许多简单问题。所有人都会认为原理图、布局和制造工艺没有问题,但不幸的是,它们有时却并不如人愿。子插件板位置错误、虚焊和错误端接或者连接的电缆,都是一些常见问题。利用DMM电阻设置来确认所有线路和连接均正确。图2所示CAN应用的简易原理图用作参考。图2 CAN应用简易原理图

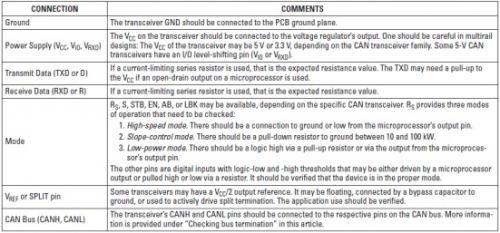

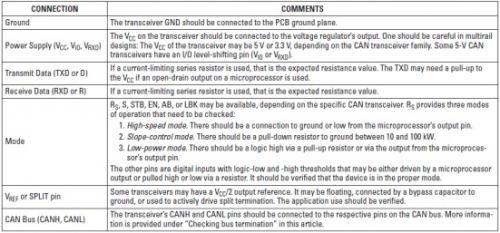

表1列举了需要检查的PCB和网络连接。收发器引脚和PCB上其他相关连接之间的电阻应为0Ω,除非设计使用表注里介绍的一些选项。例如,限流串联电阻器、总线端接电阻器或者数字I/O的上拉或下拉电阻器。

表1 PCB和CAN收发器连接总结

总线端接检查

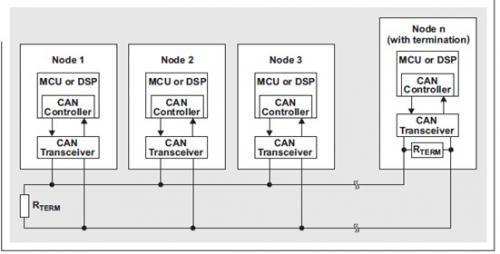

大多数CAN标准均规定使用一条单双绞线(有或者无屏蔽层),其特性阻抗(Z0)为120Ω。应使用与线路特性阻抗相同的电阻器来端接电缆两端,以防止信号反射。端接可以为电缆上总线端的单120Ω电阻器,如图3中CAN总线左侧所示;或者,它也可以位于某个端接节点内,如图3右侧所示。不得将端接电阻从总线移除。如果CAN端接电阻负载不存在,则信号完整性会受到影响,并且无法满足比特计时要求。如果总线共模电压滤波和稳压理想,则使用分裂端接,如图2所示。在该图中,每个电阻器均为60Ω,而分裂电容器范围为1 nF到100 nF,具体取决于共模滤波器所需的频率。2CANH到CANL的测得电阻应介于45Ω到65Ω之间,以达到CAN标准、两个端接电阻器的并联阻抗以及并联节点输入电阻的容差。应根据可能碰到的极端故障状态(通常为系统接地的电源电压)来确定端接电阻器的额定功率。图3 典型CAN总线

电源检查

在系统上电以前,应首先检查CAN收发器的一个或者多个电源。根据所使用的收发器类型,VCC应为3.3V或者5V。不管您相不相信,在一些情况下,丢失VCC确实为问题的根本原因。因此,我们应确保VCC存在于收发器的VCC引脚上。只需检查DMM,便可确认有电源存在。必须注意电源短路接地(不幸的是,该引脚就在VCC引脚的旁边)。显性状态(60Ω总线负载时约为60mA)和隐性状态(10mA)之间所需电流(ICC)差约为50mA。显性总线状态期间端接电阻差分电压的产生需要这50mA的电流差,并且其随总线负载变化而变化。DMM还可用在电流模式下,以验证预计ICC电源电流。由于CAN的开关性质,DMM测得的电流伪平均读取值。

建议本地旁路电容器至少应为4.7µF,以确保总线状态转换期间有足够的电源缓冲。否则,收发器的突入电流可能会引起明显的电压电源纹波。我们可以使用一个示波器来验证电源电压是稳定,还是随着总线状态变化而变化。转换期间,最好不要让收发器“饥饿”。收发器受到其限流的保护,但是,当收发器试图驱动总线至显性状态时,如果其中一条总线短路至电源或者接地,则电源电流极高。如果电压调节器无法提供这么多的电流,则电压电平降至收发器规格范围以下,甚至可能会低至触发收发器的欠压锁定状态。

CAN物理层基础知识

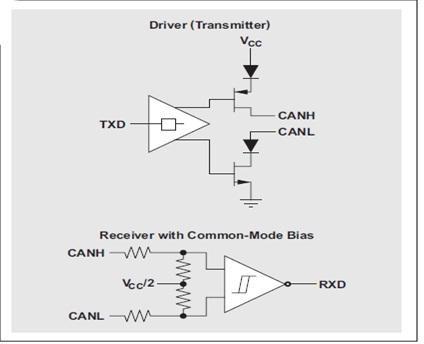

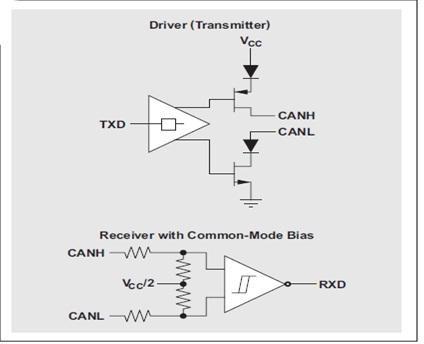

一旦完成所有基础检查,就可以检查CAN物理层的核心CAN总线了。收发器的两个关键组件便是接收器和发射器。发射器被称作CAN的驱动器。通过VCC/2共模点(约2.5V)对CAN物理层偏置,见图4。图4 简易CAN总线收发器

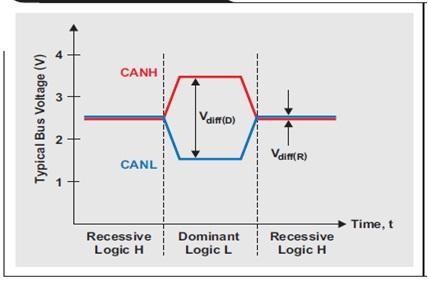

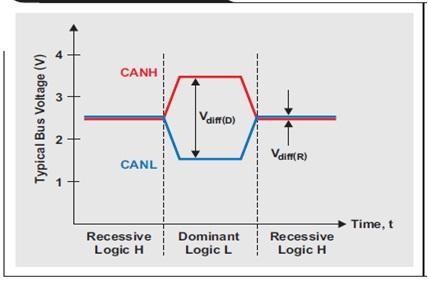

发收器将单端数字逻辑信号、TXD(或者D)和RXD(或者R)转换为差分CAN总线所要求的电平。当总线为显性时,在接收节点,其CAN标准定义的差分电压(Vdiff(D))大于1.2V,并且处于逻辑低状态。当总线为隐性时,在接收节点,其CAN标准定义的差分电压(Vdiff(R))为-120mV≤(Vdiff(R))≤ 12 mV,并且处于逻辑高状态。两种总线状态均通过收发器内共模网络偏置。图5显示了典型的总线层级。

图5 CAN总线状态

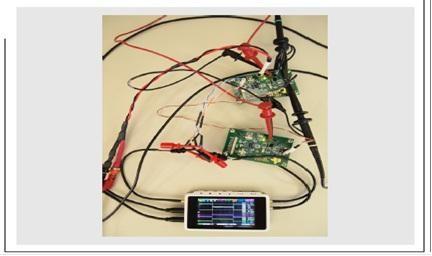

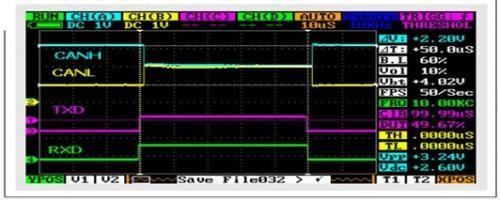

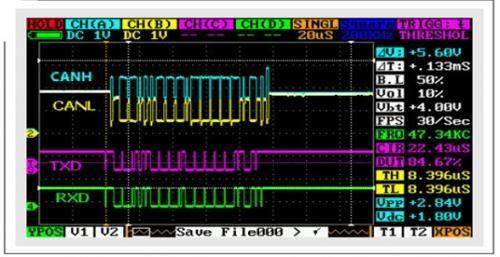

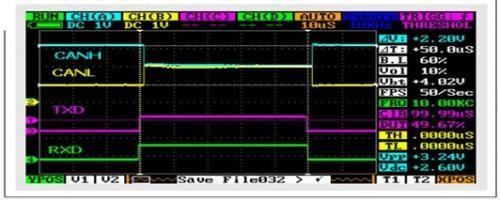

对总线进行调试时,最为有用的工具之一便是示波器。尽管单通道示波器便可看到信号,但最好还是用双或者四通道。理想情况下,可同时看到TXD、RXD、CANH和CANL,以确保收发器和总线性能如预期。进行初次调试时,只需一个低带宽示波器,因为标准CAN被限定在1Mbps。(在不远的将来,在引入拥有灵活数据速率的CAN以后,这种情况将有所改变。)如果该节点正发送数据比特流,则可在TXD输入端看到输入数据。差分CAN总线引脚(CANH/CANL)存在传输延迟,同时还存在RXD输出传输延迟。在CAN中,这些延迟均为循环时间,或者说循环延迟。如果该节点正在接收,则TXD闲置;但是总线和RXD输出会显示CAN帧。为了演示基础CAN总线工作情况,图6显示了一个示波器,它拥有两个模拟通道和两个数字通道,以及一个函数生成器。CAN总线由两个SN65HVD255D EVM组成,每个在总线上的端接电阻均为120Ω。示波器函数生成器连接至顶部EVM的TXD输入引脚。图7中,数字通道1显示了CANH信号(蓝色);模拟通道2显示了CANL信号(黄色);数字通道2显示了RXD信号(绿色)。尽管该示波器的精确度很低,但这个简单的测试表明,该CAN物理层的表现在总体上符合我们的预期。

图6 两个EVM的CAN总线调试

图7 TI CAN EVM信号

图8显示了该示波器和用于调试TI CAN演示系统的探针装置。该节点使用菊形链,并使用CANopen® D-SUB 9针连接器。一个总线外接头连接器位于图8左上方。利用它,我们可以轻松地连接模拟示波器探针至CAN总线的CANH和CANL引脚以及GND。由于探针过大,无法抓住中间CAN节点的TXD和RXD IC引脚,因此可通过连接至探针的芯片钩和一小段电缆,将这些引脚连接至示波器的数字通道。另一种方法是,给每个收发器焊接一小段线,这样示波器探针便可更容易地连接。图8 TI CAN演示系统调试

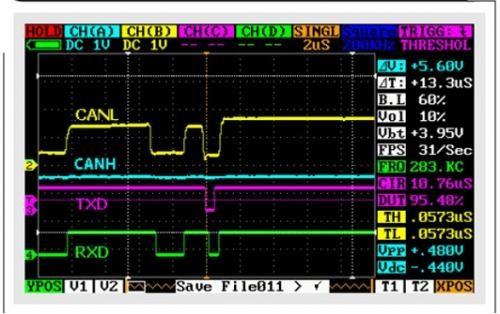

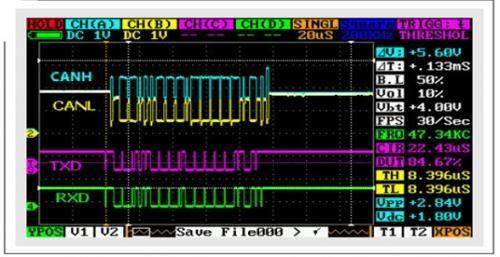

图9显示了示波器获得的CAN信号详细情况。尽管这些信号的分辨率和精度均不高,但它们可以帮助确定需要了解CAN节点工作的那些信息。中间节点的TXD触发了示波器;CANH和CANL信号差异符合预期;在CAN构架端可清楚地看到高差分电压的收到确认(ACK)位。该高压为同时并行产生ACK位的多个CAN节点的结果。轻松找出ACK位的另一个方法是其存在于RXD信号中而非TXD信号中,这意味着它由另一些节点产生。

图9 TI CAN演示系统的信号

CAN调试例子

图10显示了一个CAN演示系统,在PCB右边,连接至菊形链输出的CANH线路被损坏。出现这种情况的原因是,系统后面的一个固定螺栓摩擦PCB,而在几年的时间里该系统被运输至世界各地。当系统通过菊形链总线接口连接至其他CAN节点时,便故障无法工作。图10 带有损坏CANH线路的CAN演示系统

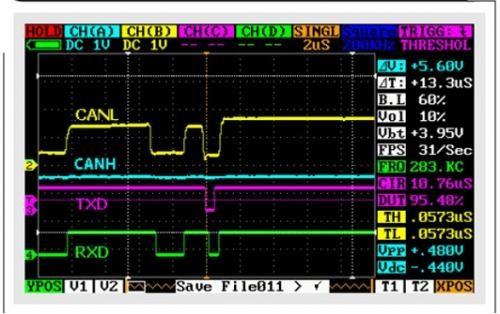

图11所示CANH信号表明了该损坏PCB线路的效果。另外,DMM连续性检查也可证实该开路。图11 PCB上CANH线路遭损坏的TI CAN信号

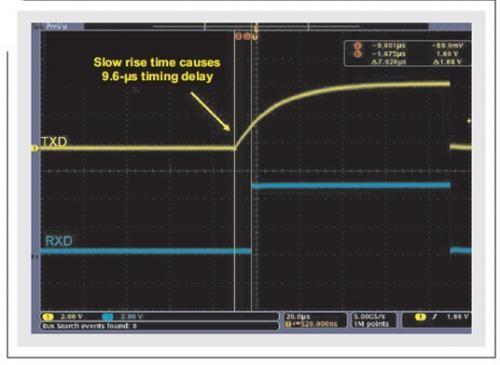

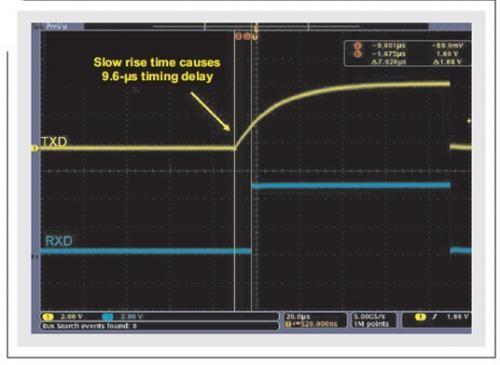

图11还突出详细显示了CAN帧的另一个重要部分,即ACK位。示波器使用单一模式,在某个单比特发现触发器时,其在右手节点的TXD引脚上被触发。该单比特为这一节点产生的ACK位,目的是确认接收到一个有效的CAN帧。所有接收节点确认收到发送节点的CAN帧。相比在TXD上看到的发送ACK位,总线上所看到的ACK位的位时间稍长。这是同时发送ACK位的多个节点的假象。影响这种长位时间的一些因素包括:通过线缆的5ns/m延迟、三个CAN节点之间的时钟计时漂移以及同时发送一个ACK位的两个节点所产生的高差分电压。如果这些因素使ACK位(空档)变得更长,并在ACK分隔符内保持显性,则其可能引起CAN误差帧。CAN总线调试的另一个例子是,在某个系统中,只有非常慢的CAN数据速率(比特计时)才会起作用。把一个示波器连接至TXD引脚,在TXD输入端显示出非常慢的上升时间,如图12所示。1Mbps的CAN数据速率下,9.6µs计时延迟相当于10比特。它的根本原因是:我们正使用一个具有开路漏极的微处理器来驱动收发器的TXD引脚。在这种情况下,没有真正的逻辑高电平驱动。仅有CAN收发器的弱内部上拉正驱动TXD引脚高,因此它的RC时间常量非常长。通过在TXD引脚上添加一个上拉电阻器,便可轻松解决这个问题。

图12 TXD引脚上慢上升时间例子

以上就是本文介绍的用实际例子分析CAN物理层基础和调试的全过程,有图文解说应该很容易理解了哦,设计人员应该可以马上让其CAN系统正常运行了。谢谢阅读。希望能帮到大家。

免责声明:本文系转载,版权归原作者所有;旨在传递信息,其原创性以及文中陈述文字和内容未经本站证实。

帮同学化妆最高日入近千 帮朋友化妆帮同学化妆最高日入近千?浙江大二女生冲上热搜,彩妆,妆容,模特,王

2023吉林省紧缺急需职业工种目录政策解读 2024张杰上海演唱会启东直通车专线时间+票价 马龙谢幕,孙颖莎显示统治力,林诗栋紧追王楚钦,国乒新奥运周期竞争已启动 全世界都被吓了一跳(惊吓全世界)热门标签

热门文章

-

和数字搭配的女孩名字(和数字搭配的女孩名字大全) 24-10-07

-

灯笼花一年开几次花 灯笼花一年开几回 24-10-07

-

冬桃苗品种 冬桃苗品种有哪些 24-10-07

-

长绒棉滑滑的冬天会不会冷(长绒棉是不是很滑) 24-10-07

-

竹子冬天叶子全干了怎么办 竹子冬天叶子干了来年还能活吗 24-10-07

-

春天移栽牡丹能开花吗(春天移栽牡丹真的不开花吗) 24-10-07

-

表示心酸的一句话 表示心酸的一句话简短 24-10-07

-

轮胎气门嘴用什么胶(轮胎气门嘴用什么胶好) 24-10-07

-

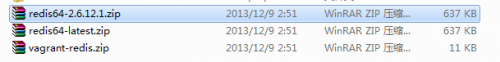

windows安装redis缓存使用图文教程(windows下redis安装步骤) 24-10-07

-

康乃馨怎么繁殖(康乃馨怎么繁殖方法) 24-10-06